# Parallel CMOS Implementation of NOR Logic in both Pull-Up and Pull-Down Networks

## Noor Ul Abedin

Assistant Professor, Dept. of ECE, Deccan College of Engineering and Technology

*Abstract-* Aware to that the implementation of CMOS logic based on NAND and NOR logic principles of pull-up and pull-down combination of transistors, this work shows how by using both the combinations of pull-up and pull-down transistors in parallel too we can realize a NOR logic. This is illustrated with the help of using DS CH software.

*Index Terms*- CMOS, NOR, Pull-up, Pull-down, Parallel and DS CH software.

#### I. INTRODUCTION

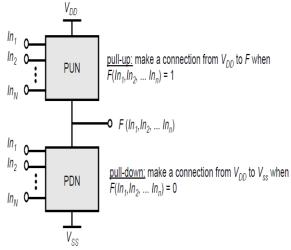

The CMOS designing/design constitute a pull-up and a pull-down network with:

- 1. Pull-up network having only PMOS transistors

- 2. Pull-down network having only NMOS transistors.

Fig. 1.0 - Pull-up and Pull-down network These fundamental approach works basically on two logics i.e. NAND and NOR logic,

| For NAND Logic         | For NOR Logic          |  |

|------------------------|------------------------|--|

| PUN-PMOS transistors - | PUN-PMOS transistors - |  |

| Parallel Connection    | Series Connection      |  |

| PDN-NMOS transistors - | PDN-NMOS transistors - |  |

| Series Connection      | Parallel Connection    |  |

|                        |                        |  |

Table. 1.0 - NAND and NOR Combination Logic

Here a two input NOR logic is been implemented and analyzed as with respect to parallel combination of the transistors in both pull-up and pull-down networks using DSCH software.

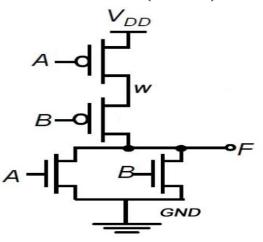

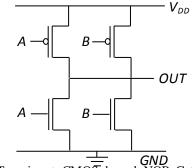

> II. BASIC NOR LOGIC PULL-UP AND PULL-DOWN NETWORKS

- A. A basic NOR logic as per the CMOS design topology follows:

- PUN- PMOS transistors- series Connection

- > PDN- NMOS transistors-Parallel Connection NOR FUNCTION ( $F = \overline{A + B}$ )

Fig. 2.0 - Two input CMOS based NOR Gate

| Ų       |         |          |

|---------|---------|----------|

| Input A | Input B | Output F |

| 0       | 0       | 1        |

| 0       | 1       | 0        |

| 1       | 0       | 0        |

| 1       | 1       | 0        |

Table. 2.0 – Truth Table of Two input CMOS based NOR Gate

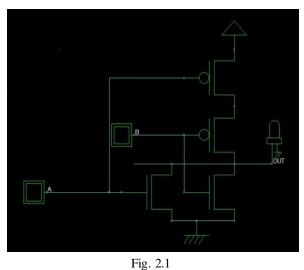

The basic NOR logic verifies the NOR truth table. Implementing the basic NOR logic using DSCH software, it is observed to the conclusive verification of the NOR logic.

> Pull-up and pull-down arrangement.

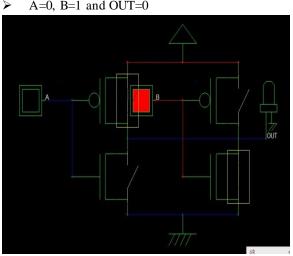

Fig. 2.2 A=0, B=1 and OUT=0

$\geq$

Fig. 2.3

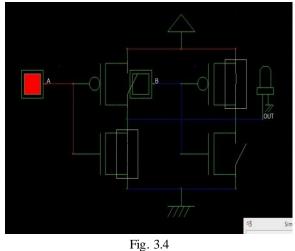

$\blacktriangleright$  A=1, B=0 and OUT=0

Fig. 2.4

$\blacktriangleright$  A=1, B=1 and OUT=0

Fig. 2.5

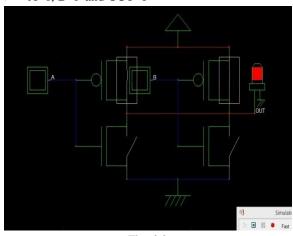

## III.PARALLEL COMBINATIONS OF TRANSISTORS IN PULL-UP AND PULL - DOWN NETWORKS FOR NOR LOGIC

Analyzing the NOR logic with parallel implementation in both Pull-up and pull-down networks.

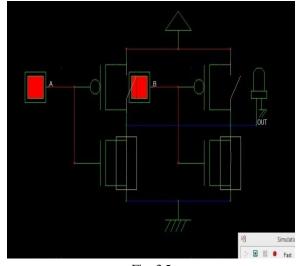

Fig. 3.0 Two input CMOS based NOR Gate using Parallel transistors combination

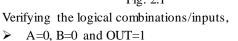

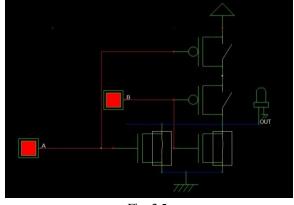

The conclusiveness obtained after verifying it on DSCH software are:

Parallel Pull-up and pull-down arrangement.

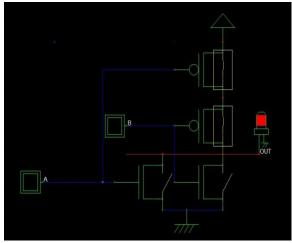

Fig. 3.1 Verifying the logical combinations/inputs, A=0, B=0 and OUT=1

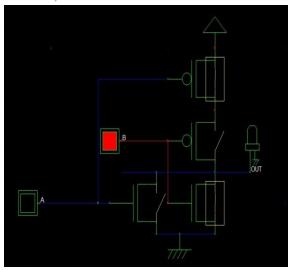

Fig. 3.3

$\blacktriangleright$  A=1, B=0 and OUT=0

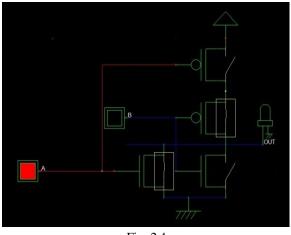

A=1, B=1 and OUT=0

Fig. 3.5

### IV. OBSERVATION/ ANAYLSIS ON DSCH CAD

The implementation of the NOR logic as done using DSCH software is been conclusively verifying all the possible logical combinations. The observation obtained is same for the fundamental/ basic CMOS design topology and for the parallel transistors implementation in both pull-up and pull-down networks.

### V. FUTURE SCOPE

Such logic implementations may be futuristic for developments of different digital logic circuits and motivate towards the existence of further different network combinations.

#### VI. CONCLUSION

It can be concluded that a CMOS NOR logic can be implemented by using the Pull-up PMOS transistors in parallel along with Pull-down NMOS transistors in parallel.

#### REFERENCES

- Design and Simulation of CMOS function by H. Abdul Wasay (International Research Journal of Engineering and Technology (IRJET))

- [2] Noor's Algorithmic Flow of Electronics and Communication Engineering by Noor Ul Abedin (International Research Journal of Engineering and Technology (IRJET))

- [3] Digital Integrated Circuits- A design perspective-2<sup>nd</sup> Ed by Jan M. Rabaey, Anantha Chandrakasan and Borivoje Nikolic (PHI)

- [4] Basic VLSI Systems and Circuits- 2<sup>nd</sup> Ed by Kamran Eshraghian, Douglas A. Pucknell (PHI)

- [5] Introduction to VLSI Circuits and Systems by John P. Uyemura- 2<sup>nd</sup> Ed (Wiley India Pvt. Ltd.)

- [6] Analog Integrated Cicuit Design by David A.

Johns and Ken Martin- 2<sup>nd</sup> Ed (Wiley India Pvt. Ltd.)

- [7] VLSI Design by Partha Pratim Sahu (McGraw Hill)

- [8] Design of Digital integrated circuits by David A. Hodges, Horace G Jackson- 3<sup>rd</sup> Ed (McGraw Hill)

- [9] Modern VLSI Design by Wayne Wolf- 4<sup>th</sup> Ed (Pearson Education)

- [10] VLSI Design by Shiva Kundarapu and Krishna Gimkala (PP)